额……老铁们,我图吧老捡垃圾的了。最近咱好像找到了麒麟960和970能效拉跨的原因了,简单和各位说一下情况。前作:【图吧杂谈】为什么说麒麟710A是个好芯片?

【图吧杂谈】麒麟990的主频提升是因为工艺吗?(附龙芯频率上不去原因补充)

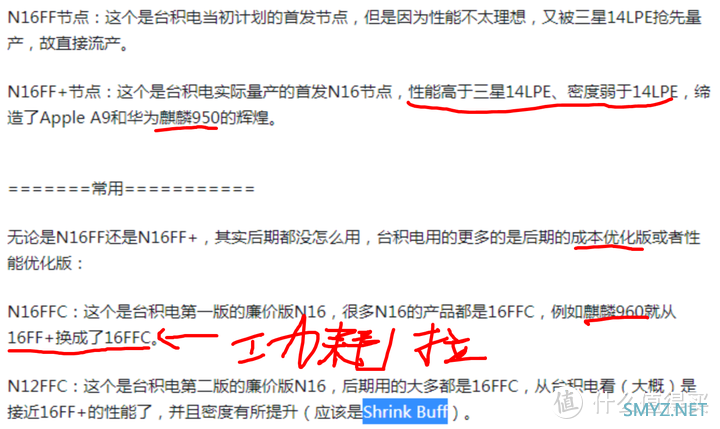

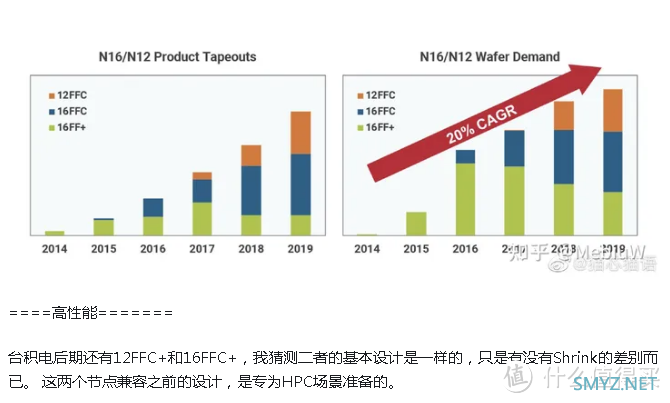

上期说到隔壁锐评龙芯的知乎用户没想到居然直接面对垃圾佬的bug提示不仅没有听取意见反而不断嘴硬甚至蹦出了典中典TSMC 14nm这样令人忍俊不禁的回复,足以证明自诩为“专业”对垃圾佬的建议不屑一顾的作者实际水平也就那么回事,并不是什么业内大佬,甚至在图吧都排不上号,所以咱简单科普了一波16nm以来的TSMC工艺发展线以及各节点之间的关系,结果就让咱发现问题了。

就是这个地方,当时咱写文章的时候还没特别注意,后期录屏视频的时候发现不对劲了:台积电主产的 16/12nm 工艺 怎么样? MebiuW的回答

源赖氏此16nm FFC非彼16nm FF+,原来工艺也能偷工减料那烧闪屏虚焊就属于活该了。

包括970的10nm FinFET想也知道都是大坑,TSMC放弃这条研发线是对的。

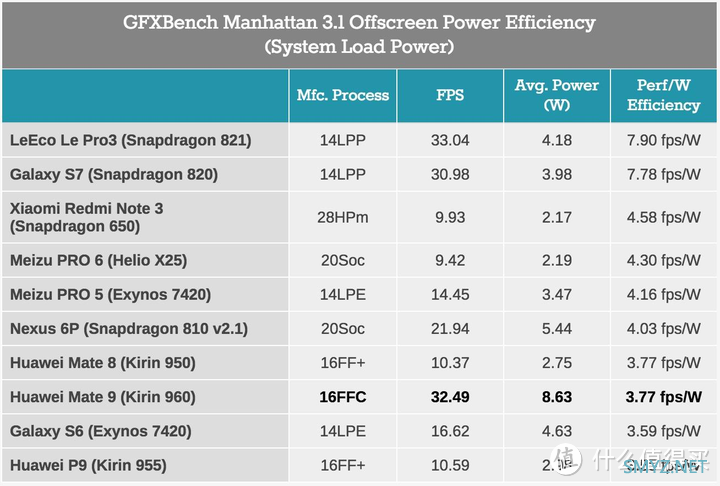

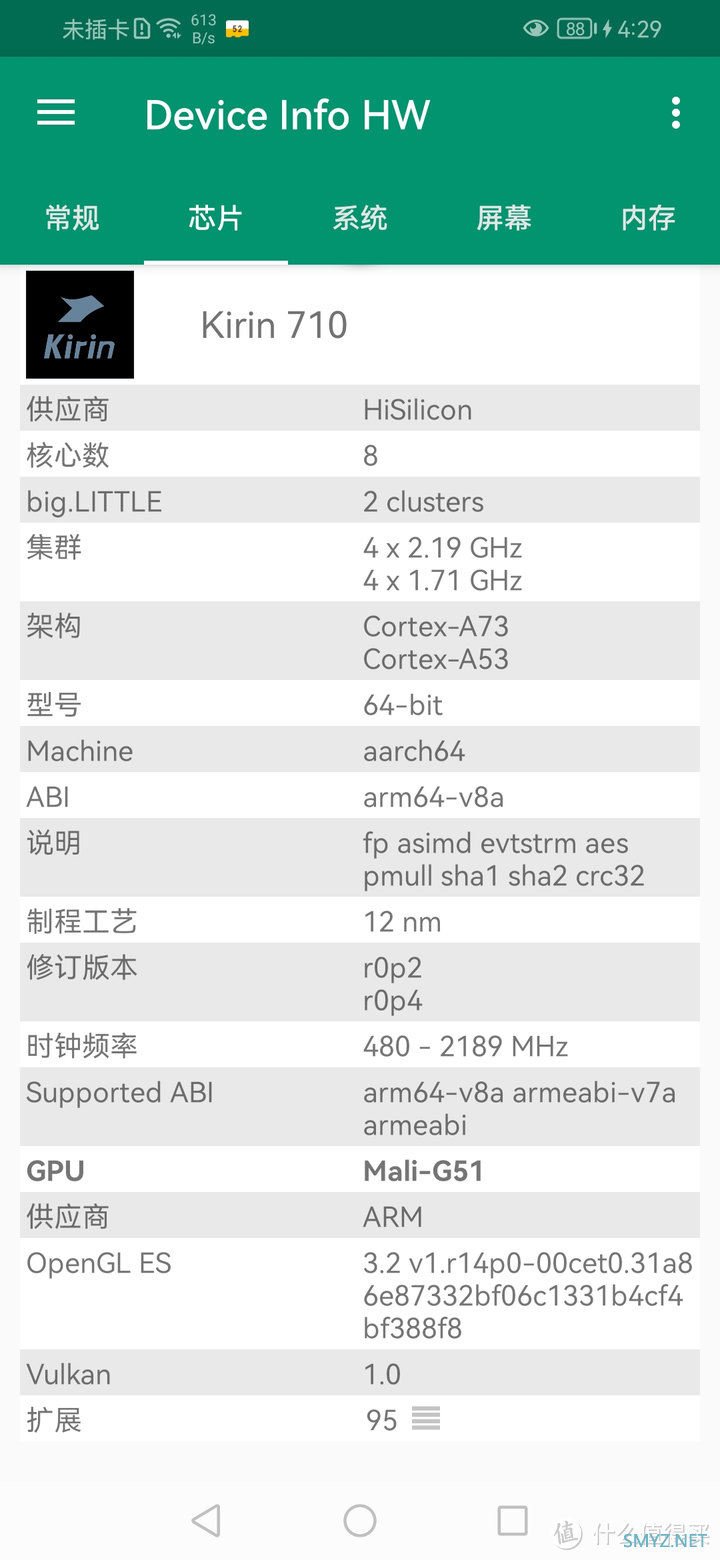

我还纳闷怎么SMIC 14nm的麒麟710A都比960 970看着能效高原来原因在这,因为麒麟710F那年头已经用上了TSMC 12nm,应该是12FFC,终于能在性能上达到麒麟955的16nm FF+节点了。这终于能解释垃圾佬内心的疑惑了,那就是麒麟955的能效为什么能高于麒麟960,至少看上去高(955性能并没差多少但是功耗远没那么高)

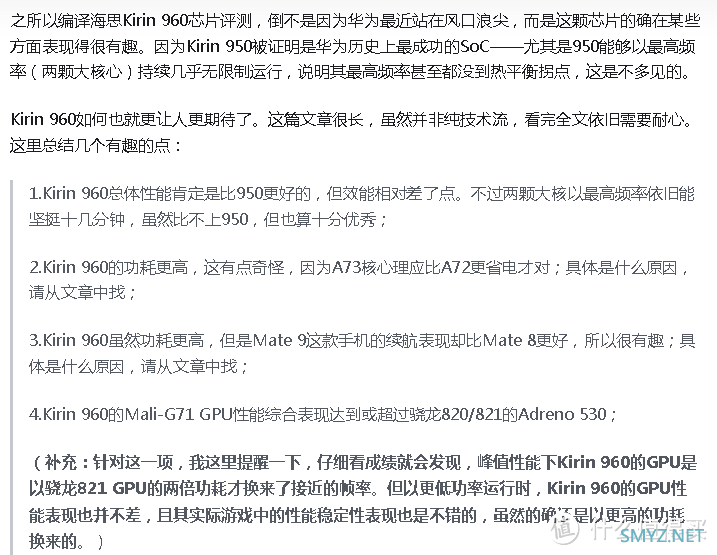

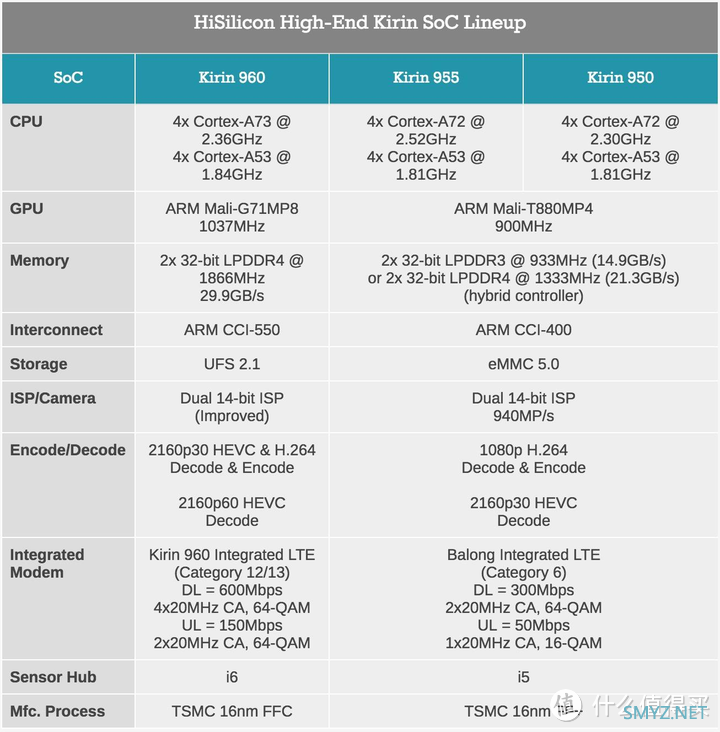

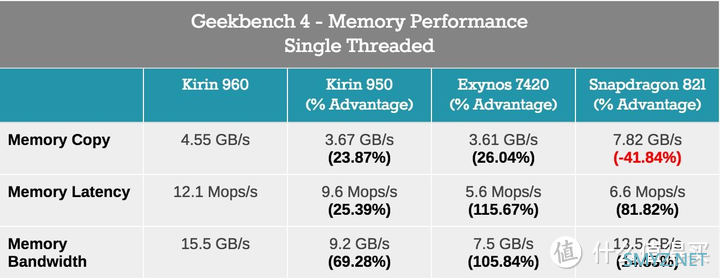

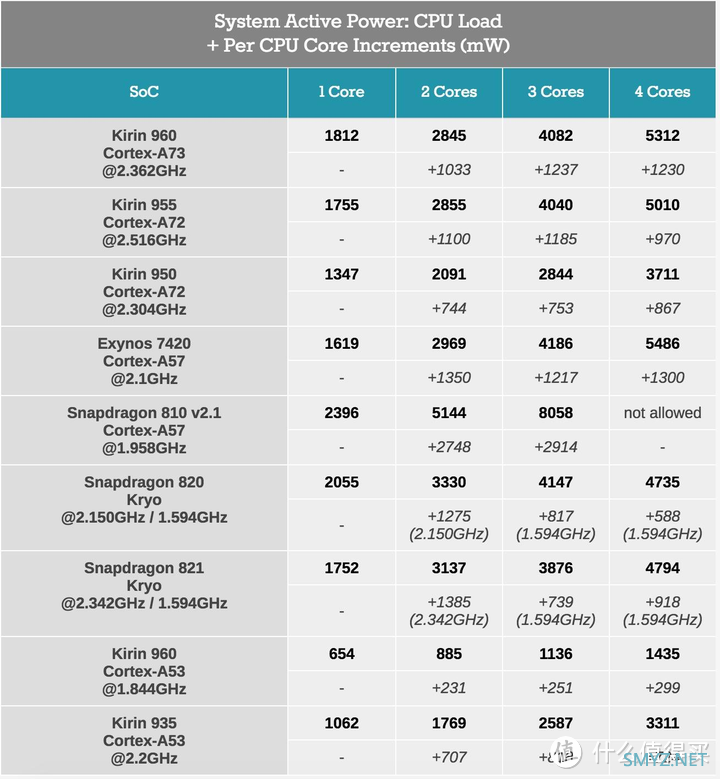

因为相比麒麟955来说麒麟960的频率并没有那么高,而麒麟955甚至不支持UFS和真正意义上的LPDDR4(兼容LPDDR4但是实际跑分只有LPDDR3水平),所以同样作为单卡4G的SOC来说麒麟960的功耗实在是令人匪夷所思。可能由于GPU堆料堆太猛了的原因导致功耗翻车 ,因为A73的CPU相比A72正常来说能效理应能效是提升的,过去咱一直是这么看的,但是现在咱终于明白过来到底是怎么回事了,那就是工艺缩水。麒麟960的功耗能效翻车完全可以归结于采用了台积电的廉价16nm工艺,这并不是工艺升级而是倒退,这就不难理解了。

顺带说下从当年的测评中找到的能效结果来看其实麒麟960的能效和950是持平的,略高于955,只能说海思尽力了,用台积电的缩水工艺还能有如此表现应该说设计方面功不可没。

不过查找过去的文章可以发现Kirin 960采用16FFC大坑工艺可能并非海思所愿,当时台积电的产能受限就连苹果都搞出了A9混用台积电16nm和三星14nm抽奖的操作,初出茅庐的海思麒麟只能在妥协中求生。

至于麒麟970采用的TSMC 10nm FinFET大雷工艺更是台积电20nm多曝拉跨工艺的升级,而不是16/12nm节点的迭代,所以麒麟970同样采用A73+A53的CPU甚至GPU从G71升级为G72也于事无补。功耗依然居高不下导致产品可靠性不足。

台积电的20nm节点究竟有多拉?高通骁龙810就采用了这个20nm工艺,结果和火龙800一样火龙810也成了典中典的功耗翻车教科书案例。结果就是大部分厂家选择拒绝使用直接从28nm跳到16nm,比如NVIDIA和海思麒麟,包括上海兆芯之类的其他采用TSMC工艺的国产芯片都是这个套路。AMD甚至宁可把显卡GPU给GF代工也不敢用台积电的20nm,可想而知这个工艺到底有多拉,即使改头换面升级10nm也本性难移。所以后期台积电取消了这条产品线的研发转而去折腾N7+EUV了,也算是及时止损拨乱反正。

PS:关于ARM A73公版: A73 处理器为移动设备及其他消费电子设备量身打造,针对设备性能及能耗所做的优化让人感到尤为兴奋:移动功率电路性能极佳,频率最高可达 2.8GHz;功耗效率提升 30%,保证最佳用户体验;内置于迄今为止体积最小的 ARMv8-A 架构;在产品开发初期,A73的目标就已经十分明确:打造能效最高、性能最强的 ARM 处理器。

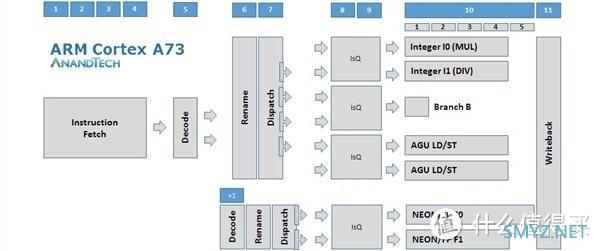

A72采用了三发射设计,A73则是双发射的,但加上其他改进,结果就是性能高于A72、功耗低于A72。整数工作负载至少节省 20% 功耗;浮点运算和存储器访问等工作负载的优化甚至更加明显,功耗的降低显著提升了用户体验。

简而言之,A73相比A72在砍了核心流水线宽的前提下在提供更高性能的前提下功耗还能更低。这个操作咱非常熟悉因为国产芯片里面国产X86的兆芯就干过这种操作:

兆芯的KX5000五道口架构采用了双发射的设计,相比之前的ZX-C(+)其实是精简了核心设计的,甚至流水线也更短,但是依然在同样的工艺下达到了相同的频率。

不过和兆芯的ZX-C和KX5000一样,A72和A73并不存在技术上的迭代关系,张江被认为是基于威盛原有以赛亚2半成品由上海兆芯团队参与完成设计,而五道口则是兆芯团队从13年成立开始完全自主设计的微架构,并在设计完成后更换工艺小改为陆家嘴,最后通过优化设计实现在16nm工艺不变前提下最大频率提高到3.3G,能效提高60%待机功耗降低50%,达到接近INTEL ATOM/银牌奔腾赛扬的能效水平。

A15、A57、A72架构上都属于Austin(奥斯汀),A5、A7、A53均属于Cambridge(剑桥), A12、A17和今天的A73则都来自于Sophia(索菲亚)——位于法国南部风景迷人地中海之滨的索菲亚科技园区(Sophia Antipolis),是欧洲最大的科技园区,ARM CPU的法国设计团队就在那儿。

从产品定位上看,A73显然要取代A72,但是从技术层面讲, 它其实是A17的进化版本,整体微架构、流水线、宽度设计都与之类似,反而和A72差别很大。

ARM有相当庞大的研发团队,可以多个研发团队分别进行研发,而英特尔以及台积电都有相应的多研发团队部署,然而国产芯片里似乎只有华为海思有相对应的能力,其他国产芯片通常只能最多同时支持一个研发团队,所以CPU架构的研发周期通常较长一般为5年一代,这也是正常的项目周期。在过去垃圾佬发现龙芯吧小吧主彭东峰就数次攻击其他国产芯片搞一些IPC无提升=性能零提升=研发能力没提升=没研发能力的经典话术,结果最近其他国产芯片纷纷拿出IPC成倍提升的新架构出来之后没动静了。

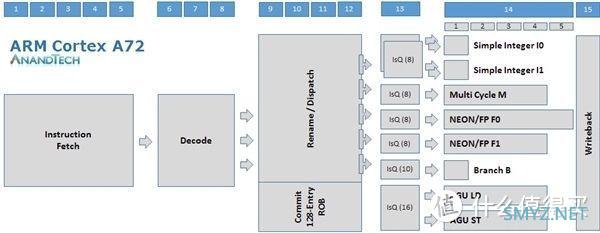

A72的架构图:

15+级乱序流水线,128位预取,3宽度解码,每时钟周期可分派最多5个微操,满足最多7个发射队列,进入8个执行流水线。

A73十分类似A17,因为顺序前端的优化流水线短得多,预取阶段也只有4级深度(A72 5级),整个流水线深度也才11-12级。

相比于A17,它将整体最大分配率从4个微操增加到了6个。NEON发射序列仍然是2个微操,但是整数部分翻番到了4个。

浮点流水线还是2条,预取监视器也是1个,但是AGU部分可同时执行载入和存储操作。整数流水线则分成了2个复杂的ALU,分别负责乘法和除法。

A73继承了A17的架构理念,优化流水线、资源和接口,以求在最低功耗下获得最大性能,并且特别注意了32/64位架构之间的平衡。

A73核心尺寸比A72最高减小25%,除了在16纳米和10纳米工艺等先进技术节点应用中发挥作用,A73 处理器在大众市场28纳米工艺技术节点上也大放异彩,大幅提高中端移动设备的性能,占用面积减少允许设备搭载更多芯片,集成更多功能或提升其它系统IP的性能,也可以减少中端移动设备的SoC及设备成本。

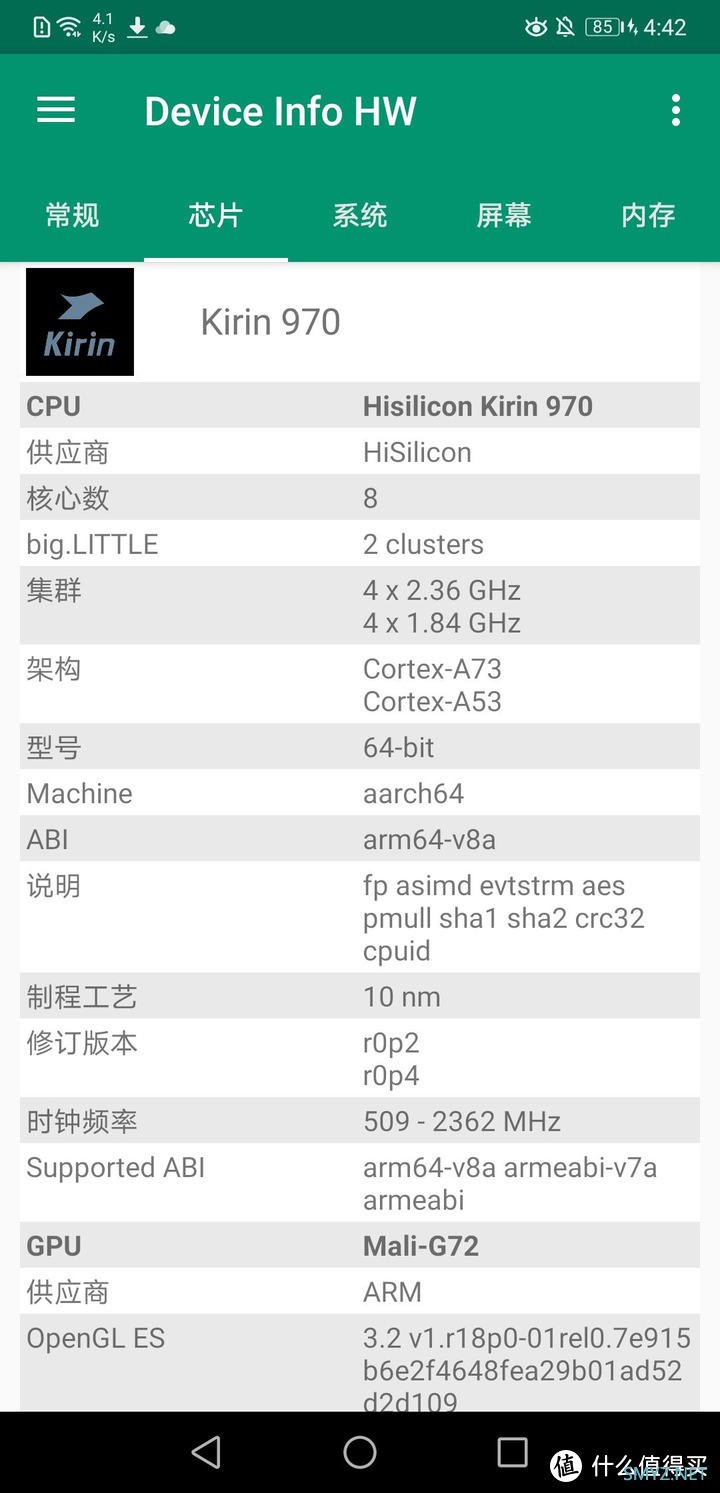

总之前作咱发现麒麟710F相比麒麟970的CPU修订版本并没有任何变化就感觉很奇怪。

毕竟从数值上来看无论是TSMC12nm还是SMIC14nm都比TSMC10nm更大,但是前者明显能效更高功耗更好,咱并不觉得砍NPU砍GPU就能实现大幅降低功耗的效果,原因就是10nm工艺实在太拉,麒麟960的16nm更是丐中丐所以结果就是垃圾佬的主力手机依然是18年380包邮麒麟955的华为P9,用了5年才换麒麟990 4G+巴龙5000。

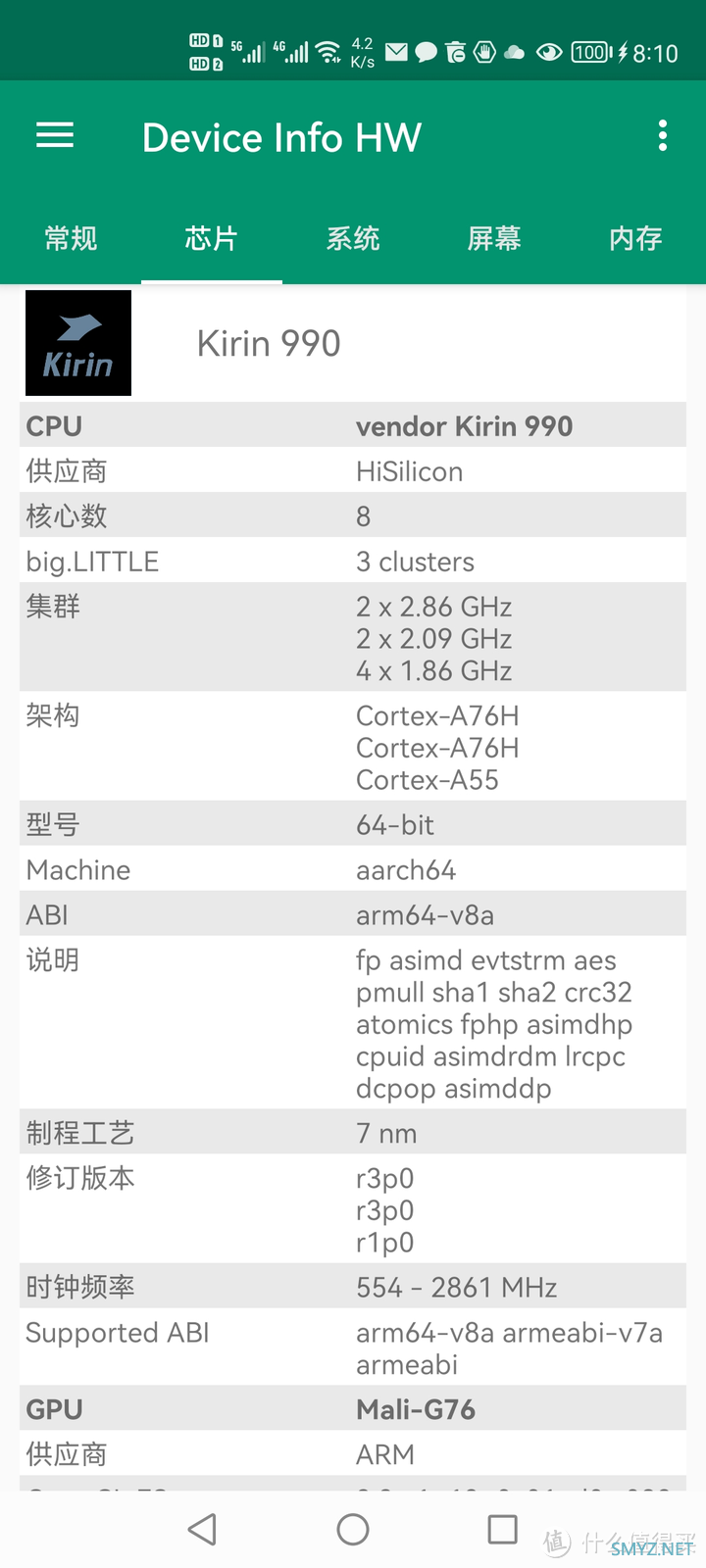

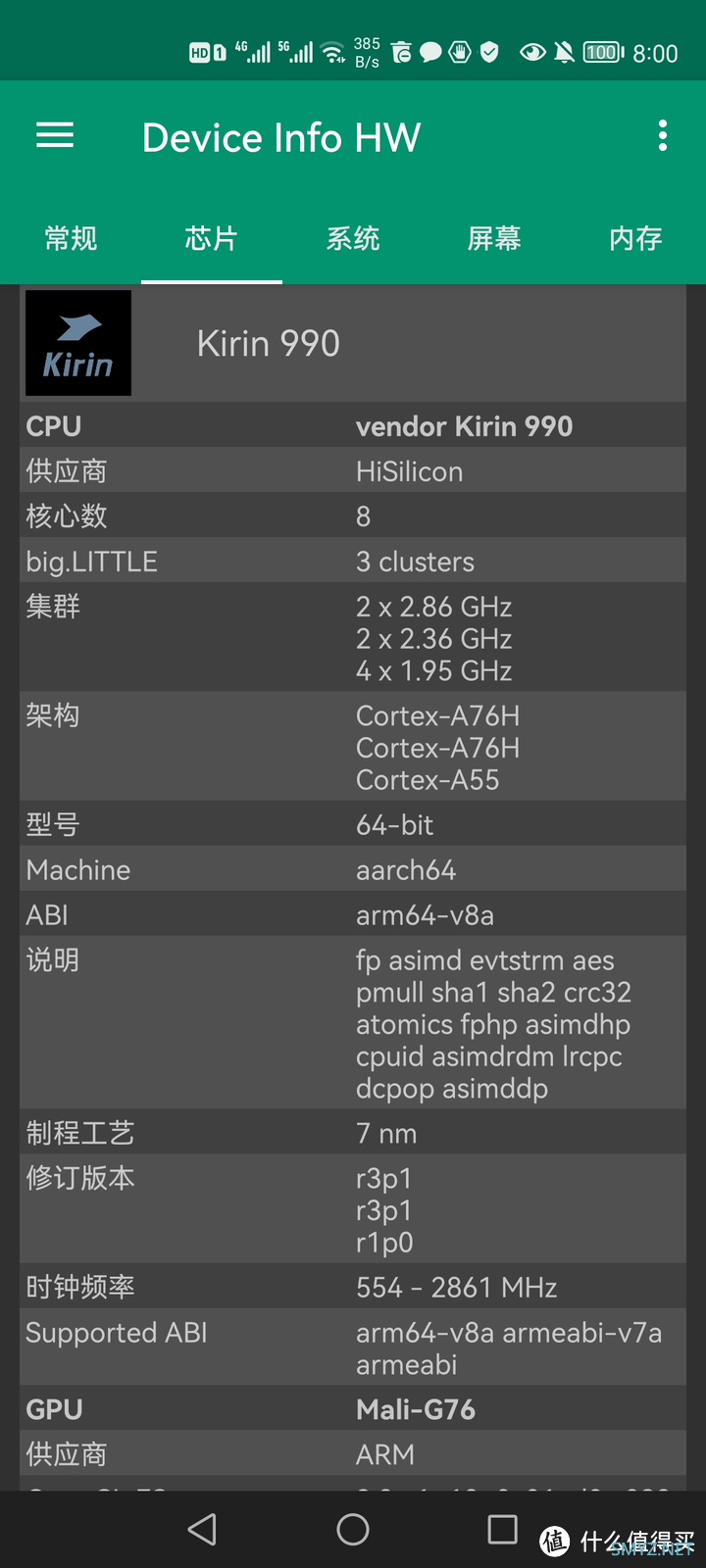

顺带说下上期咱也提到了麒麟990和990 5G的CPU步进修订版本并不一样,所以咱要说啥来着,等咱以后有了麒麟980的机会咱会提供CPU修订版本的截图的,包括麒麟960都提供一下,这样就能更有效的分析能效和工艺以及CPU架构之间的关系。

就这样,谢谢朋友们!

作者声明本文无利益相关,欢迎值友理性交流,和谐讨论~

加载中,请稍侯......

加载中,请稍侯......

网友评论